## Los bits de justificación y el fenómeno del jitter como alteración de fase primordial en los radios digitales de transmisión de datos\*

Justification's bits and jitter phenomenon as main alteration of phase in digital radio data transmission

José Gabriel Réding\*\*

José Alonso Pérez\*\*\*

Benjamín Tass\*\*\*\*

Jorge Vázquez\*\*\*\*\*

Fecha de recepción: enero de 2014 Fecha de aceptación: febrero 2014

#### Resumen

Los fenómenos de alteración de una señal digital que interfieren con su desempeño, están presentes sin importar la cantidad de filtros, elementos o dispositivos electrónicos dinámicos de alta calidad y aislamientos del entorno que se tengan. Es indispensable contar con una gestión técnica adecuada en el manejo de las alteraciones que pueda sufrir la señal original. Para corregir y alinear velocidades en las tributarias entrantes en los equipos de multiplexión de alto orden, se tiene la aplicabilidad de los principios de justificación positiva o inserción de bits o huecos que regulan dicha velocidad de lectura-escritura. En la transmisión de datos, un fenómeno conocido como fluctuación de

<sup>\*</sup> Artículo de investigación

<sup>\*\*</sup> Universidad Autónoma del Carmen, Instituto Tecnológico del Sur de Yucatán. Contacto: reding70@yahoo.com.mx

<sup>\*\*\*</sup> Universidad Autónoma del Carmen, Instituto Tecnológico del Sur de Yucatán. Contacto: japerez@pampano.unacar. mx

<sup>\*\*\*\*</sup> Universidad Autónoma del Carmen, Instituto Tecnológico del Sur de Yucatán. Contacto: btass@pampano.unacar.mx

<sup>\*\*\*\*\*</sup> Universidad Autónoma del Carmen, Instituto Tecnológico del Sur de Yucatán. Contacto: vazquez\_70@yahoo.com.mx

fase o Jitter, mismo que causa un corrimiento de la posición ideal del bit recibido, lo que lleva a una inexactitud de la señal final con respecto al ingreso original. Ningún sistema digital se debe presumir como inmune a estas alteraciones.

**Palabras clave:** bits de justificación, radio, transmisión, fluctuación, jitter.

### **Abstract**

The phenomena of alteration of a digital signal that interfere with optimal performance, are present regardless of the number of filters, or dynamic elements electronic devices of high quality and environmental isolates that are available. Because of this, it is essential to have a proper technical management in managing the changes that may occur to the original signal. To correct and align the tax rates on incoming teams high order multiplexing is the applicability of the principles of positive justification or insertion of bits or voids that regulate this speed read-write. On the other hand, data transmission, we have a phenomenon known as jitter or jitter, even causing a shift in the ideal position of the bit received ( with reference to their nominal flanks, which leads to an inaccuracy final signal from the original income. No digital system must be presumed as immune to these changes.

**Keywords**: justification bits, radio, transmission, jitter.

## 1. Transmisiones digitales de alto orden

Los sistemas de transmisión de datos, como finalidad primordial, optimizan el medio, de cable, fibra óptica o radio enlace, para enviar el mayor número de canales empleando el mismo path, es decir, proveen una optimización de los recursos con que cuenta el enlace. Al desarrollar sistemas de multiplexación empleando la frecuencia (FDM), se estaría limitando a un cierto ancho de banda, que para el caso de la voz humana en los sistemas de comunicación telefónica se normalizó de 300 Hz a 3.4 KHz [1]. Posteriormente, y tratando de simplificar el uso de los recursos en infraestructura de enlaces, se desarro-

lló el TDM o multiplexación en división del tiempo, asumiendo que la digitalización de los servicios de transmisión abrirían brecha entre los usuarios de los servicios actuales en la transmisión de datos. Bajo este criterio, los recursos se volvieron cada vez más demandados y el usuario se convirtió en un "nodo demandante" de servicios digitales especializados con una gran capacidad, tanto en velocidad como en ancho de banda.

Pero, desde que se dispuso de circuitos digitales integrados VLSI altamente confiables y asequibles, la implantación de enlaces múltiples de acceso público se convirtió en un negocio proyectado de rápido crecimiento. La generación de señales complejas trajo ventajas y contratiempos, dado que la infraestructura no contaba con los recursos técnicos suficientes para poder migrar a las técnicas de transmisión digital, que se basan en un tipo de modulación es especial conocida como PCM o modulación por Pulsos Codificados, que a su vez requiere de cuatro etapas consistentes en: filtrado, muestreo de las señales entrantes, cuantificación y codificación [1].

Los enlaces conocidos como PCM generan una señal compleja que involucra a 30 canales de voz y dos de señalización, este concepto se le conoce como primer orden y alude a la norma europea que se aplica en México.

Los enlaces PCM de primer orden generan señales complejas que alcanzan velocidades de 2.048 Mbps y utilizan par trenzado, coaxial o fibra óptica para conexión con el extremo remoto, los canales de señalización proveen la instancia reguladora que ubica las posiciones de las muestras codificadas de los canales involucrados, es decir, actúa como el sistema controlador y regulador que direcciona e integra la información originalmente muestreada al doble de la frecuencia máxima (teorema de Shannon). Al integrar cuatro tributarias de primer orden, es decir, cuatro señales entrantes de 2.048 Mbps, se genera una señal mux compleja llamada de segundo orden con una velocidad aproximada de 8 Mbps, resultado de multiplexar en tiempo las cuatro tributarias entrantes originales.

Al optimizar el uso de los medios de comunicación — par trenzado, coaxial o fibra óptica — la rentabilidad de los enlaces se incrementó, pero la técnica de multiplexado en tiempo conlleva a la inserción de tributarias provenientes de enlaces secundarios, es decir, se emplea lo que en Estados Unidos se conoce como un enlace drop-insert [2].

La jerarquización de los órdenes europeos se constituye a partir de cuatro tributarias de orden inferior, pero el aumento de niveles de multiplexación —segundo, tercero, cuarto y quinto orden, según la norma europea — conlleva a la división de tiempo de bit original de las tributarias, lo cual conduce ineludiblemente a una segmentación del tiempo de bit actual, especializando los flancos de subida y bajada para las señales digitales.

El concepto de alineamiento de flancos decisorios para la señalización y la ubicación inequívoca de las señales entrantes alude una temporización atómica para el deslinde de los periodos encubiertos en las señales muy complejas.

La temporización requerida difiere de las instancias plesiócronas tributarias, por lo que los sistemas de transmisión de altas velocidades demandan un tipo de justificación positiva. El concepto conocido como justificación positiva provee al equipo multiplexor de la capacidad de aceptación de tributarias bajo criterios temporales individuales diferentes, pero empleando técnicas de acoplamiento en tiempo, genera la señal mux compleja con una alta sincronía.

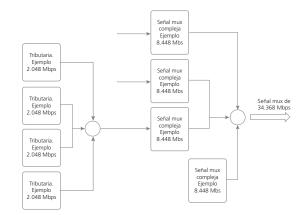

La capacidad técnica de los equipos de transmisión deben permanecer inalterables cuando las señales afluentes son controladas por una misma señal de reloj central a atómico. Bajo estas condiciones la relación de fase entre las señales es consistente, por lo que su combinación en una sola señal compleja se puede efectuar de manera casi proporcional e inalterable. En la figura 1 se muestra el diagrama a bloques de un multiplexor digital síncrono [2] [3].

Como se ha mencionado, a la entrada de un equipo de alto orden, se tienen las cuatro señales afluentes que son almacenadas en memorias intermedias con su velocidad nominal inicial. Posteriormente, cada señal es extraída de la memoria dinámica a una velocidad superior, que para la norma europea sería T/4, y pasa a un circuito combinador donde se intercalan bit a bit con las demás afluentes, sumándose además los bits de señalizacion de alarma y de sincronismo, con lo cual queda integrado el tren de pulsos de salida de orden superior a una velocidad final T — en la figura se muestra una velocidad final de 34368 Kbps—.

En la sección del lado receptor se efectúa en proceso inverso, ya que la señal de orden superior llega a un circuito separador (demultiplexor), el cual aisla los bits correspondientes a cada trama tributaria y originalmente entrante, empleando memorias de paso o intermedias que las almacenan con una velocidad T/4, haciendo uso de osciladores "amarrados" en fase, éstos elementos CLK poseen la capacidad de eliminar los espacios generados por los bits de servicio y de sincronía.

Originalmente, cuando las señales afluentes son controladas por relojes diferentes, únicos e independientes, a las tramas tributarias se les conoce como plesiocronas, es decir son señales "casi o muy cercanas" al sincronismo, pero de alguna manera no coinciden con los flancos de subida y bajadas proveidas en cada señal ingresada. La jerarquía digital sincrona (JDP o PDH: Plesiochronous Digital Herarchy) funciona en un estado donde las afluentes entrantes están casi completamente sincronizadas, lo que permite la variación en la velocidad nominal debido al ingreso no controlado de las tramas originales, lo que aparece en cualquiera de los órdenes de multiplexación, como los mostrados en la tabla 1.

Figura 1. Señal mux compleja, jerarquías básicas y drop-insert

Fuente: elaboración propia.

Tabla 1. Jerarquías bajo la norma europea

|                                                  | _                       |                                                                        | _                       |

|--------------------------------------------------|-------------------------|------------------------------------------------------------------------|-------------------------|

| Tributarias<br>(norma<br>europea)                | Señal Mux<br>resultante | Medios de<br>transmisión                                               | Nominación<br>técnica   |

| 32 canales<br>de voz<br>y dos de<br>señalización | 2.048 Mbps              | Par trensa-<br>do (cable<br>simétrico)                                 | PCM primer orden        |

| 4 tributarias<br>de 2.048<br>Mbps                | 8.448 Mbps              | Par trensa-<br>do, cable<br>coaxial, fibra<br>óptica o<br>radio enlace | PCM<br>segúndo<br>orden |

| 4 tributarias<br>de 8.448<br>Mbps                | 34.368 Mbps             | Cable<br>coaxial, fibra<br>óptica o<br>radio enlace                    | Tercer orden            |

| 4 tributarias<br>de 34.368<br>Mbps               | 139.264<br>Mbps         | Cable<br>coaxial, fibra<br>óptica o<br>radio enlace                    | Cuarto<br>orden         |

| 4 tributarias<br>de 139.264<br>Mbps              | 565 Mbps                | Fibra óptica                                                           | Quinto<br>orden         |

Fuente: elaboración propia.

Los multiplexores utilizados previamente en la transmisión por radio digital, se pueden clasificar en multiplexores digitales síncronos y multiplexores digitales asíncronos; su estudio es fundamental para el entendimiento del Jitter como un fenómeno de alteriación de señales digitales y su afectación en la transmisión de datos, específicamente en las señales empleadas por los radios digitales [3].

# 2. Sincronización de tributarias y la justificación positiva

La justificación positiva es un procedimiento empleado para eliminar o reducir al mínimo la posibilidad de error o interferencia en los enlaces digitales, es decir, provee la posibilidad de concretar la señal mux compleja síncrona a través de señales plesiócronas entrantes en un equipo multiplexor de orden superior. La justificación positiva evita la interferencia o traslape de información de una señal digital con otra de velocidad binaria ligeramente diferente (plesiócronas), el proceso de justificación positiva provee tanto de un canal de soporte en el equipo transmisor para acoplar la señal tributaria entrante, como condicionado aproximadamente a una velocidad del 0.2 % por encima de la velocidad nominal de la señal entrante.

La expresión justificación o relleno positivo es análoga a lo empleado en los procesadores de texto actuales, en cuyo caso "se justifican" los renglones ingresando espacios en blanco. Para los sistemas digitales, lo que se inserta son espacios en blanco, con lo que las velocidades plesiócronas se justifican y alinean temporalmente, es decir, se fundamenta un alineamiento de flancos de subida y bajada obteniéndose una señal sincronía de salida compleja a partir de tributarias no alineadas en tiempo e ingresadas al equipo mux de orden superior. La mayoría de las administraciones técnicas en telefonía y transmisión de datos emplean la llamada justificación positiva.

El principio básico de relleno puede ser observado en la figura 2, la cual muestra que, a partir de la señal entrante, se recupera el reloj respectivo y con ello se inscribe la señal digital en la memoria elástica dinámica, comúnmente conocida como memoria tapón.

En dicho dispositivo es posible llevar a cabo de manera simultánea los procesos de escritura y lectura, donde la frecuencia de lectura obtenida está condicionada por el sistema multiplexor y se elige más rápida en comparación con la señal tributaria, obviando las tolerancias y pausas del reloj (CLK central), dando paso a la integración de la trama de orden superior.

Iniciado el proceso y con una frecuencia de reloj (CLK) más alta, se asegura la transmisión de todos los bits entrantes de la tributaria, señal adicionada de la indicación correspondiente -bits de inicio y parada, numeración de tributaria, entre otros - . En consecuencia, la lectura sistemática procura una lectura sobre datos "no inscritos", por lo que se exige una comparación entre direcciones lógicas de locación en lectura y escritura de los registros respectivos. Para el caso de que la dirección de lectura alcance o rebase a la de escritura, se inserta un hueco mediante un circuito comparador lógico, que valida la necesidad del tal inserción empleando la frecuencia de comparación - frecuencia de lectura –, en este caso, la dirección de lectura no continua transfiriendo y la locación de escritura sigue activa y obtiene un nuevo salto.

Al activarse el bit de relleno o justificación, este no aporta información útil o trascendental para el enlace en cuestión. La indicación certera de que se ha insertado un bit de justificación y su locación actual, debe ser difundida al resto de los equipos nodos empleando los canales de comunicación convencionales, es decir, empleando los llamados bits de control de justificación. Tal consigna provee la información necesaria sobre la pertinencia, ubicación lógica del bit de relleno y la instrucción de paro de la memoria elástica, deteniendo con ello el contador de direcciones y la escritura en el registro correspondiente.

Figura 2. Justificación positiva (diagrama a bloques del lado de transmisión)

Fuente: elaboración propia.

Para la transferencia de la señal a través de la ruta de transmisión, la frecuencia de reloj no debe presentar ningún hueco. En electrónica, dicha situación se controla con un oscilador de banda estrecha o VCO (Oscilador controlado por voltaje), determinando el hueco justificador en la frecuencia de reloj.

Como se mencionó anteriormente, la presencia de los bits de justificación es indicada por los bits de control de justificación, los mismos que se generan para cada componente del canal. De manera lógica y conceptual, la justificación positiva se representa por una secuencia de tres unos, y la ausencia de tal justificación se denota por tres ceros (000). Para el caso de la señalización remota o en el extremo receptor, la secuencia 110 es considerada como una indicación de presencia de justificación y la señal 001 lo demanda la ausencia de ella.

Dada la explicación anterior, el demultiplexor ubicado en el extremo lejano, de manera lógica, debe reconocer y extraer los bits de justificación de cada señal componente, reconstruyendo la señal de una forma consistente, por lo que dichos elementos son alojados en posiciones específicas dentro de la trama o marco construido a partir de las tributarias plesiócronas [5].

### 3. Fluctuación de fase o Jiiter

El jitter describe la inestabilidad en el tiempo de los momentos del cruce con cero de la señal digital. Cuando esa modulación en fase interferente excede los límites de tolerancia definidos o normaticos, no es posible llevar a cabo un reconocimiento sin errores en la recepción. Lo anteior conlleva al análisis de los valores de jitter de la señal digital y el comportamiento del jitter propio de los equipos de transmisión, en nuestro caso de los radios digitales, para la comprensión e interpretación lógica de los espectros de la señal transmitida.

El jitter puede tener diferentes orígenes si la frecuencia de oscilación libre de un circuito de recuperación de reloj (CLK), en un regenerador, es diferente de la frecuencia nominal y, además, la señal a ser regenerada contiene una larga secuencua de ceros, entonces la fase de la señal de reloj tiende a desplazarse — efecto conocido como *drift* — hasta que nuevos impulsos sean recibidos para lograr el sincronismo, lo cual debe lograrse al analizar

los flancos correspondientes. El fenómeno anterior sucede de manera frecuente en la JDP.

En un caso de origen electrónico, el jitter se genera de manera natural en los multiplexores digitales, donde señales no síncronas entre sí y a su ingreso, deben ser combinadas sin pérdida de información, significando un reto para el diseño de circuitos multiplexores de alto orden. En este último caso, técnicas especiales (stuffing) son necesarias para minimizar el impacto sobre las señales complejas. Como análisis adicional, aunque en menor escala, el jitter puede ocurrir debido a "interferencias externas" al propio sistema de radiocomunicación, este sería el caso del fenómeno conocido como diafonía, que podría reducirse drásticamente empleando un buen diseño en el tendido de cables de transmisión, de recepción o tributarios.

En general se deben contemplar tres parámetros de interés en las mediciones del jitter en un sistema de radio transmisión de datos:

Valor del jitter tolerable en la trama de **entrada.** Es definido como la fluctuación de fase tolerable en la entrada de un sistema o equipo digital, para la cual aún no existen errores, o al menos se suponen errores mínimos en tazas de 10-12. Los valores de fluctuación de fase, tolerables al ingreso de las señales, presentan un comportamiento típico, el cual permite altos rangos de jitter en frecuencias bajas y, por otro lado, bajos límites de jitter para frecuencias altas. Este fenónmeno se aprecia pseudocorrecto para los sistemas multiplexores de alto orden, siendo la realidad técnica contraria a ese supuesto. Las mediciones de jitter tolerable en una tributaria entrante son realizadas modulándo secuencias pseudoaleatorias con jitter senoidal y verificándose en la salida del sistema de prueba; registrán-

- dose y tasándose a partir de que valores de jitter empiezan a generarse errores en la transmisión original.

- 2. Función de transferencia de jitter. Describe la característica del jitter de salida en relación al jitter de entrada, a través de un circuito de dos puertas a lo largo del eje de frecuencias. La medición es realizada con una secuencia pseudoaleatoria o patrón tipo 1000 uno seguido de cuatro ceros u otras secuencias repetitivas modeladas con jitter senoidal. El punto más importante bajo ese contexto es determinar si existe ganancia de jitter en alguna frecuencia con un patrón lógico inducido.

- 3. Jitter propio. Se hace una distinción entre el jitter de salida sin considerar jitter en la entrada del sistema. La medición se realiza con secuencias pseudoaleatorias, es decir, se descarta la alteración de entrada y salida, quedando sólo el jitter generado en el propio sistema. La investigación del jitter tolerable en una entrada y de la función de transferencia, requiere generadores de jitter capaces de producir altos valores de jitter en la entrada.

Los medidores deben poder generar una señal de referencia con un límite muy bajo, además de ser capaces de medir valores altos de jitter en frecuencias bajas, mientras que la precisión de medición no debe ser influida por el jitter intrínseco. Los medidores empleados deben poseer un alto grado de precisión en cualquier rango de frecuencias, especialmente en las altas, debido a que se esperan resultados técnicos significativos al realizar dichas pruebas.

### 4. Tipos de fluctuación de fase

Al pretender diseñar sistemas de transmisión de datos se idealizó la pertienencia en el envío de señales digitales, por lo que el jitter se encumbró como un fenómeno oscilante aparecido en los relojes (CLK) de los equipos de multiplexión, logrando su cúspide de atención en los altos órdenes. Las fluctuaciones u oscilaciones no se pueden eliminar completamente, pero existen subsistemas capaces de reducirlos. Según recomendaciones de organizaciones de telecomunicaciones internacionales, se deben tener valores referidos en la tolerancia del fenómeno, proveyendo servicios de alta calidad y disponibilidad en los enlaces de transmisión de datos. Se han subclasificado los siguientes tipos de jitter:

- 1. No sistemático o propio. Conocido como jitter no sistemático o aleatorio, no es correlativo y no es acumulativo a lo largo de la trayectoria del enlace; dicha característica minimiza la influencia que tiene en la calidad de la transmisión [6].

- 2. Sistemático. También se le denomina jitter, dependiente de la secuencia o condicionado por el sistema. Posee gran importancia para los nivels de calidad de la transmisión, pues constituye una porción importante del jitter total y debe ser cuantificado.

- 3. Causado por la justificación. Nombrado como jitter de relleno o de justificación, generalmente aparece en consecuencia al relleno por justificación, adicionándose una baja frecuencia [6] [7].

- 4. Jitter por tiempo de espera. Este es considerado como un fenómeno aditivo del causado por justificación. El jitter por tiempo de espera posee una frecuencia muy baja y pasa sin modificarse por los circuitos de adecuación del reloj en los

multiplexores, lo que conlleva a errores en la transmisión de datos.

El jitter sistemático o propio del enlace, es causado por la presencia de ruido aleatorio en los componentes eléctricos, electrónicos y mecánicos presentes en el enlace. Una fuente trascendental de este tipo de jitter es el ruido generado por los circuitos lógicos debido a la incertidumbre en el análisis de los flancos de transición.

El nombrado como jitter sistemático se detecta en las evaluaciones inadecuadas de la interferencia intersimbólica, en las variaciones de los límites de excitación de los circuitos electrónicos tanque y en las conversiones de modulación, específicamente en los tipos AM y PM — modulaciones en amplitud y en fase — .

El jitter provocado por el proceso de justificación se genera debido a la inserción de las señales tributarias y aparece generalmente en los equipos multiplexores de alto orden, es decir, el hecho de contar con señales entrantes plesiócronas, compensa las diferencias de las velocidades entre las señales digitales, apareciendo con ello el jitter.

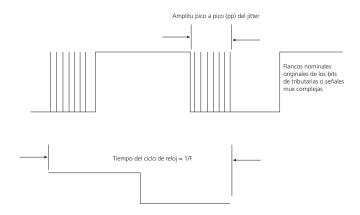

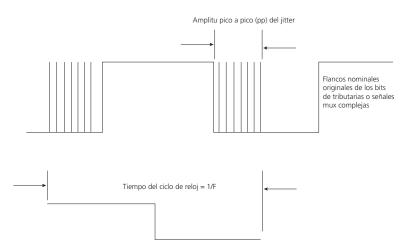

De la figura 3, dos parámetros rigen al jitter, a saber:

- La amplitud indica la magnitud de la diferencia de fase entre los flancos ideales y aquella fase de la señal en el instante eventualmente analizado.

- 2. La frecuencia, cuyo análisis indica la velocidad con que se ejecuta la variación de dicho fenómeno.

Figura 3. Jitter y su amplitud pico a pico

Fuente: elaboración propia.

Como punto final, el jitter se mide en UI (unidades internacionales) que indican la duración de un bit de un ciclo de reloj o de 360 grados de desviación o desfasamiento, no aplicando ningún criterio de análisis de velocidad en el equipo de transmisión de datos.

### **Conclusiones**

La ubicuidad de los equipos de multiplexación y la creciente demanda de servicios digitales, tanto en capacidad como en velocidad, hace necesario el estudio, comprensión y generación de procedimientos lógicos o electrónicos para reducir el impacto que provoca la generación aislada de señales de reloj. Las señales ingresadas plesiócronas con la causa fundamental de la instalación y optimización de método de justificación positiva, dando en consecuencia y como una de las causas principales, la generación del jitter en los enlaces de datos. Los bits de justificación y el jitter comparten prioridad en las instancias de multiplexaje de alto orden, lo que conlleva a una atención técnica en el diseño de sistemas de altas velocidades digitales.

### Referencias

- [1] R. L. Freeman, Fiber optic Systems for telecommunications, John Wiley & Sons, 2002.

- [2] Inttelmex, "140 Mb/s Line Terminating Magazine", Ericsson. Vol. 27, pp. 2-1, 8-2. México.

- [3] A. Carlson, P. B. Crilly, J. C. Rutledge, Sistemas de Comunicación, 2007, México: Mc Graw Hill 859, 2007.

- [4] S. Ángeles-Herrera, L. C. Arredondo-Ugalde, N. M. Martínez-Bárcenas, Diseño y optimización del enlace de comunicaciones entre Los Cabos y Puerto Vallarta por medio de fibra óptica submarina, Tesis del IPN.

- [5] E. Herrera Pérez, Introducción a las Telecomunicaciones Digitales, 4ta reimpresión, Ed. Limusa Noriega Editores, 2003.

- [6] B. McNurlin, R. J. Sprague, Information Systems Management in Practice, 2a. ed. Vol. 1 New York: Prentice Hall, 2004.

- [7] Redes ópticas, redes de larga distancia, Capítulo 7. Disponible en http://www. gco.upv.es/es/webdocente/redes/ transpar/ro7nuevo.pdf